Основой КМОП элементов является инвертор, построенный на двух комплементарных (дополняющих) МОП транзисторах (n -МОП и p -МОП) с изолированным затвором и индуцированным каналом. Особенностью такой схемы (рис. 4.17 ) является то, что входное напряжение управляет не только ключевым, но и нагрузочным транзистором.

На рис. 4.5.2. приведены стоко-затворные характеристики используемых транзисторов. Транзистор с n -каналом (VТ n ) начинает проводить ток, если на его затвор подается положительное напряжение, а транзистор с р -каналом (VТ p) – если на его затвор подается отрицательное напряжение по отношению к истоку.

Важно, что оба транзистора имеют «пятку» на своих стоко-затворных характеристиках. Таким образом, если мы хотим, чтобы схема работала при положительном напряжении питания (+E П ), то в качестве ключевого транзистора необходимо использовать VТ n , а в качестве нагрузочного – VТ p .

Рис. 4.17.1. КМОП инвертор

Рис. 4.5.2. Стоко-затворные характеристики КМОП транзисторов

Инвертор (рис. 4.17 ) построен так, что исток VТ p соединен с E n , а исток VТ n – с землей. Затворы VТ n и VТ p объединяются и служат входом инвертора, стоки VТ n и VТ p также объединяются и служат выходом инвертора. При таком включении будут справедливы следующие формулы для определения напряжения затвор-исток VТ n и VТ p: U зип = U вх, U зир = U вх -Е п

U зип – напряжение затвор-исток n -канального транзистора (VТ n );

U зир – напряжение затвор-исток р -канального транзистора (VТ р ).

При рассмотрении работы инвертора будем полагать, что VТ n и VТ p обладают идентичными характеристиками и пороговое напряжение U Пп = ½U Пр ½=1,5В.

U Пп - пороговое напряжение n -канального транзистора;

U Пр - пороговое напряжение p -канального транзистора.

Рассмотрим работу КМОП инвертора по его ХВВ (рис. 4.18-а ), на которой можно выделить четыре участка и зависимости U ЗИ = f (U BX ) (рис. 4.18-б ).

Участок 1: U 0 вх £ U Пп . При этом U зип = U вх и VТ n закрыт, U зир = U вх - Е п < U Пр и VТ p открыт.

Рис. 4.18. Характеристики КМОП инвертора:

а) ХВВ, б) U ЗАТВОР-ИСТОК = f(U ВХ); в) I ПОТР = f(U BX)

VТ n закрыт), VТ p находится в глубоком насыщении, на выходе при этом будет напряжение, близкое к E П (U 1 ВЫХ » E П).

Участок II: U П > U ВХ > U Пп,

где U П - напряжение, при котором происходит переключение схемы

и U ВЫХ = 0,5(U 1 - U 0). U ЗИП = U ВХ > U Пп и VТ n начинает открываться, U ЗИР = U ВХ -Е П < U Пр и VТ p открыт.

На этом участке ½U ЗИП ½< ½U ЗИР ½, поэтому VТ p будет оставаться в насыщении, а VТ n – в активном режиме.

VТ n .

Ток, протекающий в схеме, создает падение напряжения на канале VТ p , за счет этого напряжение на выходе начинает уменьшаться. Однако с ростом входного напряжения на этом участке выходное напряжение снижается мало, так как VТ p все еще находится в насыщении.

Точка U П : U ВХ = U П =0,5Е П;

U ЗИП =U ВХ = U П > U Пп , и VТ n открыт; 0,5Е П < U Пр и VТ p открыт.

В этой точке |U ЗИП |=|U ЗИР | следовательно, равны и сопротивления каналов обоих транзисторов. Таким образом, на выходе будет напряжение, равное половине напряжения источника питания (U ВЫХП =0,5E П). Этой точке соответствует вертикальный участок на характеристике. В этот момент схема потребляет максимальный ток, так как оба транзистора открыты. При малейшем изменении входного напряжения выходное напряжение резко меняется.

Участок III: Е П - ½U Пр ½ > U ВХ > U П ; U ЗИП = U ВХ > U Пп и VТ n открыт; U ЗИР = U ВХ -Е П < U Пр и VТ Р открыт, но с ростом U ВХ становится все менее и менее открытым.

На этом участке U ЗИП > |U ЗИР |, и поэтому VТ n находится в насыщении, a VТ p – в активном режиме.

Ток, потребляемый схемой, определяется в этом случае транзистором VТ p .

Выходное напряжение на этом участке равно падению напряжения на канале VТ n . Так как VТ n находится в насыщении, то это падение невелико, и с ростом U BX оно все более и более уменьшается.

Участок IV: Е п > U вх > Е п - ½U Пр ½; U зип = U вх > U Пп и V n открыт; U зир = U вх -Е п >U зип и VТ p закрыт.

В этом состоянии схема практически не потребляет тока (так как VТ p закрыт). VТ n находится в глубоком насыщении, на выходе при этом будет напряжение, близкое к нулю (U вых » 0).

Как видно из ХВВ (рис 4.5.1а ), КМОП элементы обладают хорошей помехоустойчивостью. Помехоустойчивость по нулю и единице равны. Это объясняется тем, что точка переключения (U вх = U П )лежит точно в центре диапазона изменения входного напряжения (Е П >U вх > 0). При Е П = +5В максимальное значение помехи может достигать 1,5В. С ростом E П абсолютная помехоустойчивость увеличивается. Помехоустойчивость КМОП элементов составляет примерно 30% от Е П (U 0 вх.макс » 0.3Е П , U 1 вх.мин » 0.7Е П ).

Так как на входе КМОП инвертора стоят МОП транзисторы с изолированным затвором, то входное сопротивление очень велико (10 12 ¸10 13 Ом). Поэтому по входу такие схемы практически не потребляют тока.

Выходное сопротивление КМОП схем мало как в состоянии Лог. 0, так и в состоянии Лог. 1, так как один из транзисторов VТ n или VТ p обязательно будет открыт. Таким образом, выходное сопротивление определяется сопротивлением канала открытого МОП транзистора и составляет 10 2 ¸10 3 Ом.

Высокое входное и малое выходное сопротивления обуславливают высокий статический коэффициент разветвления по выходу. Коэффициент разветвления будет ограничиваться сверху только требованиями по быстродействию. Так как каждый вход схемы обладает определенной емкостью, то с ростом коэффициента разветвления будет расти емкость нагрузки, которая, в свою очередь, будет увеличивать время переключения элемента.

Таким образом, с уменьшением рабочей частоты коэффициент разветвления будет увеличиваться. В связи с вышесказанным ясно, что входная и нагрузочная характеристики теряют свой смысл. Нагрузочная характеристика имеет значение только при сопряжении КМОП элементов с элементами других типов.

Малое выходное сопротивление элемента в обоих состояниях позволяет быстро перезаряжать емкость нагрузки. Это обуславливает малые времена задержек при включении и выключении схемы. Практически времена задержек равны 50 ¸ 200 нс.

Рис. 4.5.1в поясняет процесс потребления тока схемой.

В статическом положении КМОП схемы потребляют очень маленький ток (10 -6 -10 -7 А).

В основном ток потребляется при переключении схемы, в то время, когда U ЗИП и ½U ЗИР ½> U ПОР и оба транзистора VТ n и VТ p открыты (участки II и III на ХВВ) Однако величина этого тока меньше, чем у ТТЛ схем, так как объемные сопротивления открытых МОП транзисторов превышают сопротивления открытых биполярных транзисторов. По этой причине в схемах КМОП отсутствует ограничивающий резистор.

При переключении схемы расходуется также ток на заряд емкости нагрузки. Величина этого тока может быть определена как I=CEf П где f П – частота переключения схемы.

К преимуществам КМОП схем можно также отнести возможность работы при различных напряжениях питания (3‑15В). При повышении напряжения питания абсолютная помехоустойчивость будет увеличиваться, однако будет увеличиваться и потребляемый ток (участки II и III на ХВВ станут шире). При напряжении питания + 5В уровни сигналов КМОП схем становятся совместимы с уровнями ТТЛ При этом надо, однако, следить, чтобы U 1 вх.мин для КМОП схем было бы больше E П - |U ПР | длянадежного запирания VТ p . Для этой цели часто выход ТТЛ через резистор подключают к E П .

Работа КМОП схем на схемы ТТЛ осуществляется, как правило, через монтажные схемы.

На рис. 4.19 приведена схема базового элемента типа КМОП. Элемент реализует функцию 4И-НЕ. Транзисторы расположены таким образом, что при любой комбинации входных сигналов в схеме не будет протекания сквозного тока. Аналогичным образом строятся элементы типа ИЛИ-НЕ (рис. 4.20) .

В таких схемах из-за последовательного включения транзисторов в одном из плеч увеличивается выходное сопротивление в одном из состояний. Поэтому такие элементы имеют различные времена включения и выключения. Для элемента И-НЕ время включения больше времени выключения, а для элемента ИЛИ-НЕ – наоборот.

Рис. 4.19. Реализация функции 4И-НЕ на КМОП

Рис. 4.20. Реализация функции 4ИЛИ-НЕ на КМОП

Из-за очень высокого входного сопротивления даже статический заряд способен создать пробивное напряжение. Для защиты от высоковольтных зарядов статического электричества на входах схем КМОП имеется (внутри микросхемы) специальная схема защиты (рис. 4.21) .

Рис. 4.21. КМОП-инвертор со схемой защиты затвора от статического электричества

Диоды VD1, VD2 и VD3 защищают изоляцию затвора от пробоя. Диоды VD4 и VD7 защищают выход инвертора от пробоя между р и n областями. Диоды VD5 и VD6 включены последовательно между шинами питания для защиты от случайной перемены полярности питания.

Типичными представителями КМОП схем являются элементы серии К564, которые характеризуются следующими параметрами:

Е П =3¸15В; U 0 =0,01В (при Е П =5В и I н =0); U 1 =4,99В (при Е П =5В и I н =0); I 0 вх =0,2мкА; I 1 вх =0,2мкА; I П =0,17мА (при Е П =10В, F =100кГц и С н =50пФ); t з =80нс; I 0 вых =0,9мА (при U 0 вых =0,5В и Е П =10В); I 1 вых =0,9мА (при U 1 вых =Е П -0,5В и Е П =10В); С н = 200пФ; С вх =12пФ.

Специального внимания при подготовке требует индивидуальный эксперимент (УИРС).

Для проектирования цифровых ИС кроме биполярных п-р-п- и p-n-p-транзисторов используются также униполярные полевые и -канальные транзисторы (рис. 5.17,а), которые называются МОП-транзисторами (МOS-transistors; MOS - Metal-Oxide-Semiconductor - металл-окисел-полупроводник). В общем случае полевой транзистор имеет четыре электрода: исток S (Source), сток D (Drain), затвор G (Gate) и подложка SS (Substrate). Вывод затвора в изображении полевых транзисторов смещается ближе к истоковому выводу. Изображение канала с обогащением штриховой линией символизирует отсутствие проводимости между стоком и истоком при нулевом напряжении затвор-исток. На рис. 5.17,а символами "+" и "-" обозначены полярности напряжений на электродах для нормального режима работы полевого транзистора. Подложка обычно подключается к истоку или к одному из полюсов источника питания.

На рис. 5.17,6 показана схема включения пары комплементарных транзисторов (транзисторов с разными типами каналов), представляющая собой электронный ключ - инвертор (ЛЭ НЕ). Особенностью данного ключа является отсутствие тока через транзисторы в статическом состоянии, так как при любом значении входного сигнала один из последовательно включенных транзисторов закрыт. Ключ потребляет ток только при его переключении на интервале времени, в течение которого изменяется входной сигнал. На этом интервале оба транзистора

открыты, так как входной сигнал имеет значения приводит к значениям разностей напряжений между затворами и истоками и -канальных транзисторов, значительно отличающимися от нулевых. Наибольший ток протекает при

Полевые транзисторы позволяют построить не только цифровые, но и аналоговые ключи для коммутации двуполярных аналоговых сигналов, что невозможно сделать на биполярных транзисторах. На рис. 5.17,в показан основной элемент такого аналогового ключа (вместо потенциала земли для коммутации Двуполярных сигналов следует подать отрицательное напряжение При значениях оба транзистора закрыты (сопротивление закрытого ключа составляет ротни ключ разомкнут, а при открывается один из транзисторов в зависимости от полярности коммутируемого входного напряжения В этом Случае сопротивление между полюсами ключа проставляет от единиц до сотен Ом в зависимости от типа (сопротивленйе открытого ключа). Чем меньше зависимость величины напряжения коммутируемого сигнала, тем выше линейность ключа. При проектировании аналоговых ключей принимают меры по улучшению их линейности. Вход и выход аналогового ключа неразличимы - входом будет тот полюс ключа, на который подан коммутируемый сигнал.

Разработаны три основные технологии изготовления ИС на полевых транзисторах:

МОП технология (n-MOS technology),

МОП технология p-MOS technology),

КМОП технология CMOS technology; CMOS - Complementary MOS).

Все эти технологии постоянно совершенствуются с целью увеличения быстродействия и степени интеграции элементов на кристалле. К настоящему времени разработано несколько десятков этих технологий.

Схемотехника КМОП ИС. Первые КМОП ИС серии были разработаны фирмой в 1968 г. , затем была выпущена серия вытесненная впоследствии ( серией с улучшенными характеристиками. Данные серии ИС выпускают многие зарубежные фирмы, например, серии Серии серии серий и др. Общим

недостатком ИС всех этих серий является их низкое быстродействие (время задержки сигналов достигает сотен не) и малые значения выходных токов.

В 1981 г. фирмами Motorola и National Semiconductor были разработаны ИС серий близкие по физическим параметрам к сериям В частности, быстродействие этих КМОП и ТТЛ серий одинаково (среднее время задержки вентиля не). Еще большее быстродействие было достигнуто в КМОП сериях разработанных в 1985 г. фирмой Texas Instruments Inc. (). Положительные свойства как ТТЛ ИС, так и КМОП ИС были реализованы фирмой в ИС серии ВСТ (1987 г.), изготовляемых по BiCMOS-технологии технология с размещением биполярных и КМОП транзисторов на одном кристалле с уровнями входных и выходных сигналов ИС, совместимых с ТТЛ-уровнями) .

В табл. 5.9 приведено соответствие отечественных и зарубежных серий КМОП ИС. Напряжение питания у КМОП ИС можно изменять в широких пределах - чем выше напряжение питания, тем больше быстродействие ИС. По выполняемым функциям и (или) нумерации выводов ИС серий 4000 в большинстве своем отличаются от ТТЛ ИС аналогичного функционального назначения. Функциональный ряд ИС серий включает в себя часть ИС как ТТЛ серий 54/74, так и КМОП серий с одинаковыми номерами во всех этих сериях имеют одинаковое функциональное назначение и нумерацию выводов).

На рис. 5.18, а показаны цепи диодной защиты входов и выходов ЛЭ от электростатического напряжения у ИС серии а на рис. 5.18,6 - у ИС серии Такую защиту входов и выходов имеют все цифровые ИС, кроме преобразователей уровней напряжений которых используется другой вариант защиты входов (рис. 5.19). При первом варианте защиты входов уровни входных сигналов не должны превышать напряжения питания из-за открывания диода, включенного между входом и полюсом При втором варианте защиты уровни входных сигналов могут в несколько раз превышать значение не выводя ИС из строя (избыточное напряжение гасится на резисторе). В этом случае ИС работает как понижающий преобразователь уровня логической 1. Входная цепь обеспечивает также защиту от отрицательных значений напряжений входных сигналов. В

(см. скан)

дальнейшем цепи защиты входов и выходов, как правило, показываться не будут.

Различие между сериями (рис. 5.19,а) и (рис. 5.19,6) заключается в наличии на выходах ИС последней дополнительных буферов для развязки ИС от внешней среды. Вместо серии в настоящее время выпускается серия с небуферированными выходами, имеющая аналогичные электрические параметры (UB - Unbuffered, В - Buffered). Наличие в серии CD40005 дополнительных выходных буферов приводит к увеличению задержек сигналов в ЛЭ, но улучшает переключательные характеристики. Сравнительная характеристика этих серий приведена в табл. 5.10.

Таблица 5.10. (см. скан) Параметры ИС серий CD4000B и CD4000UB

Реализация аналогового ключа показана на рис. 5.20. При значении сигнала ОЕ = 1 (ОЕ - Output Enable) ключ открыт, а при закрыт. В закрытом состоянии ключ характеризуется большим выходным импедансом и принято говорить, что выход находится в Z-cостоянии. Вместо

потенциала земли можно подать отрицательное напряжение но при этом должно выполняться условие

Схема двухвходового представлена на рис. 5.21. Выходной каскад на двух комплементарных транзисторах является буферным каскадом, так как он изолирует все внутренние связи от выхода ЛЭ. Различие между небуферированной и буферированной сериями наглядно видно из рис. 5.22, где представлены выполняющие одинаковые функции Другое схемотехническое исполнение ЛЭ 2И-НЕ показано на рис. 5.23.

Универсальный набор элементов, состоящий из двух комплементарных пар МОП-транзисторов и инвертора, реализован в (рис. 5.24). Данный набор позволяет пользователю с помощью внешних соединений выводов ИС получать аналоговые коммутаторы и

аналоговый двухканальный коммутатор (рис. 5.25) - соединены выводы 2 и 9; 4 и 11; 3 и 6; 8, 10 и 13; 1, 5 и 12;

три инвертора - соединить выводы 2, 11 и 14; 4, 7 и 9; 8 и 13 (выход НЕ со входом 6); 1 и 5 (выход НЕ со входом 3); 10 - вход выход НЕ;

3ИЛИ-НЕ - соединить выводы 4, 7 и 9; и 11; 5, 8 и 12 (выход ЛЭ со входами 3, 6 и 10);

3И-НЕ - соединить выводы 2, 11 и 14; 4 и 8; 5 и 9; 1, 12 и 13 (выход ЛЭ со входами 3, 6 и 10);

ЛЭ, реализующий функцию соединить выводы 2 и 14; 4, 8 и 9; 1 и 11; 5, 12 и 13 (выход

ЛЭ, реализующий функцию соединить выводы 2 и 14; 7 и 9; 4 и 8; 1, 11 и 13; 5 и 12 (выход ;

инвертор с Z-состоянием выхода, выполняющий функцию

При и Z-состояние выхода при соединить выводы 8, 11 и 13;

По сравнению с ТТЛ ИС следует отметить следующие достоинства КМОП ИС серий 4000 (серий 561 и 1561):

малая мощность потребления в диапазоне частот до (в статическом режиме мощность потребления составляет на вентиль);

большой диапазон напряжения питания можно использовать нестабилизированный источник питания; очень высокое входное сопротивление ( большая нагрузочная способность на частотах до

малая зависимость характеристик от температуры. К недостаткам КМОП ИС серий 4000 (серий 561 и 1561) следует отнести:

повышенное выходное сопротивление (0,5 ... 1 кОм); большое влияние емкости нагрузки и напряжения питания на время задержки, длительность фронтов и потребляемую мощность;

большие времена задержек и длительности фронтов; большой разброс всех параметров.

Графики зависимостей рассеиваемой мощности от частоты для КМОП и ТТЛ ИС пересекаются на некоторой частоте, поскольку у ТТЛ ИС динамическая мощность очень слабо зависит от частоты переключения. На предельно допустимых частотах мощность потребления КМОП ИС оказывается такого же порядка, что и у ТТЛ ИС.

В статическом режиме (без перегрузки) у КМОП ИС уровни выходных сигналов значительно отличаются от уровней У КМОП ИС в отличие от типовых значений Требования к уровням входных сигналов также значительно различаются: у КМОП ИС в отличие от Соответственно различаются пороги переключения: для КМОП BС и 1,2 В для ТТЛ BС. Это вызывает определенные трудности при использовании в одном устройстве ТТЛ и уровень

При Способы согласования уровней будут рассмотрены в § 5.6.

В сериях выпускаются КМОП ИС двух типов: серии не согласованные по входам с ТТЛ ИС, и серии согласованные по входам с ТТЛ ИС (не требующие дополнительного преобразования уровней). Эти серии различаются выполнением входных и выходных цепей ИС, показанных на рис. 5.26,а для ИС серий на рис. 5.26,б - для ИС серий на рис. 5.27 - для ИС серий и на рис. 5.28 - для ИС серий Пороги переключения у ИС серий находятся между , а у ИС серий порог переключения равен при требовании к уровням входных сигналов, задаваемом неравенствами

Помехоустойчивость ИС серий приведена в табл. 5.11, из которой видно, что она значительно выше, чем у ТТЛ серий (см. табл. 5.5). Предельные значения параметров ИС этих серий указаны в табл. 5.12, а рекомендуемые условия эксплуатации

(см. скан)

В табл. 5.13 .

Интегральные схемы КМОП серий, имеющие одинаковые номера (у зарубежных ИС) или одинаковые буквенно-цифровые обозначения (у отечественных ИС раздельно по группам серий 176/561/564/1561 и 1564/1554), выполняют одинаковые функции и совпадают по разводке внешних выводов. В дальнейшем на рисунках для ИС КМОП серий будет указываться название ИС только одной конкретной серии, хотя аналогичные ИС могут быть и в других сериях.

Рис. 5.29 (см. скан)

На рис. 5.29 представлены ЛЭ И-НЕ, И, НЕ, ИЛИ-НЕ и сумма по модулю два, выпускаемые отечественной промышленностью. На графических обозначениях указаны номера аналогов зарубежных ИС. Логические элементы серии 176 приведены на рис. 5.30. Применение было рассмотрено выше при описании ее зарубежного аналога комплементарные пары транзисторов, G - затвор, стоки р-канального и n-канального транзисторов, SP и SN - истоки

(кликните для просмотра скана)

p-канального и n-канального транзисторов). Зарубежные ЛЭ, не имеющие в настоящее время отечественных аналогов, показаны на рис. 5.31 и 5.32.

Рис. 5.32 (см. скан)

Параметры ИС КМОП серии приведены в табл. , а в табл. П2.3 - параметры ИС серий 4000 , которые в первую очередь следует учитывать при проектировании цифровых и микропроцессорных устройств. Параметры отечественных ИС серий 176, 561 и 1561 можно найти в справочниках , а ИС серии 1554 - в . Полезный справочный материал по ИС КМОП серий имеется в .

Интегральные схемы серий 54.АС11000/74.АС11000.

Для уменьшения уровня помех у быстродействующих КМОП ИС, возникающих при переключении ЛЭ, предпочтительнее использовать центральное расположение выводов питания на

кристалле, причем выходы ИС следует располагать на той стороне, где находится общий вывод питания (GND). Фирма выпустила серии где число И указывает на центральное расположение выводов питания ИС, а числа порядковый номер ИС, как и в остальных сериях На рис. 5.33 приведены ЛЭ этих серий.

Интегральные схемы серий SN54BCT/SN74BCT.

Как указывалось выше, ИС данных серий изготовляются по BiMOS технологии. Входные цепи ИС выполняются по схеме, приведенной на рис. 5.34,а, что делает входы этих ИС совместимыми с ТТЛ-уровнями входных сигналов.

В микропроцессорных системах в большом количестве используются шинные драйверы и приемопередатчики, причем в каждый момент времени в активном состоянии находится приемопередатчик или драйвер только одного внешнего устройства, а остальные - в Z-состоянии. Драйверы и приемопередатчики, выполняемые по ТТЛ технологиям, в Z-состоянии выходов потребляют ток того же порядка, что и в активном состоянии выходов, хотя не выполняют большую часть времени полезной работы.

Основная цель разработки BiMOS ИС и заключалась в резком снижении потребляемого тока в Z-состоянии выходов ИС, предназначенных для проектирования внешних устройств микропроцессорных систем. На рис. показана схема -состоянием выхода, выполненного по BiMOS технологии входная цепь, показанная на рис. 5.34,а).

Неиспользуемые входы ИС.

При проектировании цифровых устройств на ИС могут использоваться не все их входы. Исходя из логики работы разрабатываемого устройства, на эти входы следует подать либо логический уровень 0, либо уровень 1. Логический уровень 0 как в ТТЛ, так и в КМОП ИС подается подключением неиспользуемого входа к корпусу Логический уровень 1 подается на неиспользуемые входы подключением их к источнику напряжения питания (ТТЛ ИС) или (КМОП ИС), однако входы ТТЛ ИС серий 54/74, , в которых используются многоэмиттерные транзисторы, рекомендуется подключать к источнику питания через токоограничивающий резистор для защиты от скачков напряжения, возникающих, например, при включении питания.

Логические КМОП (КМДП) инверторы

Микросхемы на комплементарных МОП транзисторах (КМОП-микросхемы) строятся на основе МОП транзисторов с n- и p-каналами. Один и тот же входной потенциал открывает транзистор с n-каналом и закрывает транзистор с p-каналом. При формировании логической единицы открыт верхний транзистор, а нижний закрыт. В результате ток через КМОП схему не протекает. При формировании логического нуля открыт нижний транзистор, а верхний закрыт. И в этом случае ток от источника питания через микросхему не протекает. Простейший логический элемент — это инвертор. инвертора, выполненного на комплементарных МОП транзисторах, приведена на рисунке 1.

Рисунок 1. Принципиальная схема инвертора, выполненного на комплементарных МОП транзисторах (КМОП-инвертор)

В результате этой особенности КМОП-микросхем, они обладают преимуществом перед рассмотренными ранее видами — потребляют ток в зависимости от поданной на вход тактовой частоты. Примерный график зависимости потребления тока КМОП-микросхемы в зависимости от частоты ее переключения приведен на рисунке 2

Рисунок 2. Зависимоть тока потребления КМОП микросхемы от частоты

Логические КМОП (КМДП) элементы "И"

Схема логического элемента "И-НЕ" на КМОП микросхемах практически совпадает с упрощенной схемой "И" на ключах с электронным управлением, которую мы рассматривали ранее. Отличие заключается в том, что нагрузка подключается не к общему проводу схемы, а к источнику питания. Принципиальная схема логического элемента "2И-НЕ " , выполненного на комплементарных МОП транзисторах (КМОП), приведена на рисунке 3.

Рисунок 3. Принципиальная схема логического элемента "2И-НЕ" , выполненного на комплементарных МОП транзисторах (КМОП)

В этой схеме можно было бы применить в верхнем плече обыкновенный , однако при формировании низкого уровня сигнала схема постоянно потребляла бы ток. Вместо этого, в качестве нагрузки используются p-МОП транзисторы. Эти транзисторы образуют активную нагрузку. Если на выходе требуется сформировать высокий потенциал, то транзисторы открываются, а если низкий — то закрываются.

В приведённой на рисунке 2 схеме логического КМОП-элемента "И", ток от источника питания на выход КМОП-микросхемы будет поступать через один из транзисторов, если хотя бы на одном из входов (или на обоих сразу) будет присутствовать низкий потенциал (уровень логического нуля). Если же на обоих входах логического КМОП-элемента "И" будет присутствовать уровень логической единицы, то оба p-МОП транзистора будут закрыты и на выходе КМОП микросхемы сформируется низкий потенциал. В этой схеме, так же как и в схеме, приведенной на рисунке 1, если транзисторы верхнего плеча будут открыты, то транзисторы нижнего плеча будут закрыты, поэтому в статическом состоянии ток КМОП-микросхемой от источника питания потребляться не будет.

Условно-графическое изображение КМОП логического элемента "2И-НЕ" показано на рисунке 4, а таблица истинности приведена в таблице 1. В таблице 1 входы обозначены как x 1 и x 2, а выход — F .

Рисунок 4. Условно-графическое изображение логического элемента "2И-НЕ"

Таблица 1. Таблица истинности КМОП-микросхемы, выполняющей "2И-НЕ"

| x1 | x2 | F |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Рисунок 5. Принципиальная схема логического элемента "ИЛИ-НЕ", выполненного на комплементарных МОП транзисторах

В схеме КМОП логического элемента "2ИЛИ-НЕ" в качестве нагрузки используются последовательно включенные p-МОП транзисторы. В ней ток от источника питания на выход КМОП микросхемы будет поступать только если все транзисторы в верхнем плече будут открыты, т.е. если сразу на всех входах будет присутствовать низкий потенциал (). Если же хотя бы на одном из входов будет присутствовать уровень логической единицы, то верхнее плечо двухтактного каскада, собранного на КМОП транзисторах, будет закрыто и ток от источника питания поступать на выход КМОП-микросхемы не будет.

Таблица истинности логического элемента "2ИЛИ-НЕ" , реализуемая КМОП микросхемой, приведена в таблице 2, а условно-графическое обозначение этих элементов приведено на рисунке 6.

Рисунок 6. элемента "2ИЛИ-НЕ"

Таблица 2. Таблица истинности МОП микросхемы, выполняющей логическую функцию "2ИЛИ-НЕ"

| x1 | x2 | F |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 0 |

В настоящее время именно КМОП-микросхемы получили наибольшее развитие. Причём наблюдается постоянная тенденция к снижению напряжения питания данных микросхем. Первые серии КМОП-микросхем, такие как К1561 (иностранный аналог C4000В) обладали достаточно широким диапазоном изменения напряжения питания (3..18В). При этом при понижении напряжения питания у конкретной микросхемы понижается её предельная частота работы. В дальнейшем, по мере совершенствования технологии производства, появились улучшенные КМОП-микросхемы с лучшими частотными свойствами и меньшим напряжением питания, например, SN74HC.

Особенности применения КМОП-микросхем

Первой и основной особенностью КМОП-микросхем является большое входное сопротивление этих микросхем. В результате на ее вход может наводиться любое напряжение, в том числе и равное половине напряжения питания, и храниться на нём достаточно долго. При подаче на вход КМОП-элемента половины питания открываются транзисторы как в верхнем, так и в нижнем плече выходного каскада, в результате микросхема начинает потреблять недопустимо большой ток и может выйти из строя . Вывод: входы цифровых КМОП-микросхем ни в коем случае нельзя оставлять неподключенными!

Второй особенностью КМОП-микросхем является то, что они могут работать при отключенном питании. Однако работают они чаще всего неправильно. Эта особенность связана с конструкцией входного каскада. Полная принципиальная схема КМОП-инвертора приведена на рисунке 7.

Рисунок 7. Полная принципиальная схема КМОП-инвертора

Диоды VD1 и VD2 были введены для защиты входного каскада от пробоя статическим электричеством. В то же самое время при подаче на вход КМОП-микросхемы высокого потенциала он через диод VD1 попадёт на шину питания микросхемы, и так как она потребляет достаточно малый ток, то КМОП микросхема начнёт работать. Однако в ряде случаев этого тока может не хватить для питания микросхем. В результате КМОП микросхема может работать неправильно. Вывод: при неправильной работе КМОП микросхемы тщательно проверьте питание микросхемы , особенно выводы корпуса. При плохо пропаянном выводе отрицательного питания его потенциал будет отличаться от потенциала общего провода схемы.

Четвёртая особенность КМОП-микросхем &mdash это протекание импульсного тока по цепи питания при ее переключении из нулевого состояния в единичное и наоборот. В результате при переходе с ТТЛ микросхем на КМОП микрохемы-аналоги резко увеличивается уровень помех. В ряде случаев это важно, и приходится отказываться от применения КМОП микросхем в пользу или BICMOS микросхем.

Логические уровни КМОП-микросхем

Логические уровни КМОП-микросхем существенно отличаются от . При отсутствии тока нагрузки напряжение на выходе КМОП-микросхемы совпадает с напряжением питания (логический уровень единицы) или с потенциалом общего провода (логический уровень нуля). При увеличении тока нагрузки напряжение логической единицы может уменьшается до 2,8В (U п =15В) от напряжения питания. Допустимый уровень напряжения на выходе цифровой КМОП микросхемы (серия микросхем К561) при пятивольтовом питании показан на рисунке 8.

Рисунок 8. Уровни логических сигналов на выходе цифровых КМОП-микросхем

Как уже говорилось ранее, напряжение на входе цифровой микросхемы по сравнению с выходом обычно допускается в больших пределах. Для КМОП-микросхем договорились о 30% запасе. Границы уровней логического нуля и единицы для КМОП-микросхем при пятивольтовом питании приведены на рисунке 9.

Рисунок 9. Уровни логических сигналов на входе цифровых КМОП-микросхем

При уменьшении напряжения питания границы логического нуля и логической единицы можно определить точно так же (разделить напряжение питания на 3).

Семейства КМОП-микросхем

Первые КМОП-микросхемы не имели защитных диодов на входе, поэтому их монтаж представлял значительные трудности. Это семейство микросхем серии К172. Следующее улучшенное семейство КМОП микросхем серии К176 получило эти защитные диоды. Оно достаточно распространено и в настоящее время. Серия К1561 завершает развитие первого поколения КМОП микросхем. В этом семействе было достигнуто быстродействие на уровне 90 нс и диапазон изменения напряжения питания 3 ... 15В. Так как в настоящее время распространена иностранная аппаратура, то приведу иностранный аналог этих КМОП микросхем — C4000В.

Дальнейшим развитием КМОП-микросхем стала серия SN74HC. Эти микросхемы отечественного аналога не имеют. Они обладают быстродействием 27 нс и могут работать в диапазоне напряжений 2 ... 6 В. Они совпадают по цоколёвке и функциональному ряду с , но не совместимы с ними по логическим уровням, поэтому одновременно были разработаны КМОП микросхемы серии SN74HCT (отечественный аналог — К1564), совместимые с ТТЛ микросхемами и по логическим уровням.

В это время наметился переход на трёхвольтовое питание. Для него были разработаны КМОП-микросхемы SN74ALVC с временем задержки сигнала 5,5 нс и диапазоном питания 1,65 ... 3,6 В. Эти же микросхемы способны работать и при 2,5 вольтовом питании. Время задержки сигнала при этом увеличивается до 9 нс.

Наиболее перспективным семейством КМОП-микросхем в настоящее время считается семейство SN74AUC с временем задержки сигнала 1,9 нс и диапазоном питания 0,8 ... 2,7 В.

Интегральные микросхемы транзисторно-транзисторной логики представляют собой микросборки малой степени интеграции, построенные на биполярных транзисторах. Основным их минусом является малое количество на один кристалл, а также критичность к напряжению питания и достаточно большой ток потребления.

На схеме чуть выше изображен простой логический элементов - 3И – НЕ . В его основе лежит обычный биполярный многоэмиттерный транзистор VT1. Уровень логического нуля на его выходе появится в случае наличии высоких уровней на всех трех эмиттерах одновременно. VT2 берет на себя функцию инвертирования (элемент НЕ), а многоэмиттерный VT1 является логическим элементом 3И.

Несмотря на перечисленные минусы самая популярная серия ТТЛ, К155 пользуется огромной популярностью и сегодня, посмотрите сколько радиосамоделок можно собрать на .

Серия К155 является самой огромной серией ТТЛ. В ней более 100 микросборок выполняющих различные логические функции и операции (И, ИЛИ, НЕ, И – НЕ, ИЛИ – НЕ, триггеры, регистры, счётчики, сумматоры.

Уровень логической единицы в микросхемах этой ТТЛ серии лежит в диапазоне напряжений от 2,4 V до 5 V), а уровень логического нуля не более 0,4 V.

Почти все микросборки этой серии, выпускаются в стандартном 14 выводном корпусе. С точкой или выемкой ключа, обазначающей первый вывод. 7-й вывод это корпус или минус. 14 лежащий напротив первого, это плюс.

Следующим шагом в эволючии К155 стала серия К555, в которой базовый ТТЛ принцип сохранен, но в коллекторные переходы транзисторов добавлены . Поэтому К555 серию назвали ТТЛШ (ТТЛ и диод Шоттки). В ТТЛЩ потребляемая мощность снизилась где-то в 2 раза, а быстродействие резко возрасло.

Микросхемы КМОП |

Буква К в начале аббревиатуры расшифровывается как - комплементарный . На практике это говорит о том, что в микросборке используются пары с одинаковыми параметрами, но один транзистор имеет затвор n-типа, а другой соответственно p-типа. Еще их называют CMOS (Complementary Metal-Oxide Semiconductor).

На рисунке приведен пример классического базового логического элемента НЕ. То есть если на вход придет единица, то на выходе будет уже логический ноль и наоборот.

Элемент 2И – НЕ . Из парочки этих логических элементов легко получить , а из нескольких триггеров - счетчик, регистр и элементарный запоминающие устройства.

И теперь о ложке дегтя: на максимальной рабочей частоте КМОП элементы заметно уступают другой логикой на биполярных транзисторах (ТТЛ) и они оффигенно чувствительны к статическому электричеству.

Микросхемы на основе КМДП структур

Цифровые ИМС на основе КМДП структур все шире используются при разработке разнообразных электронных схем, на что имеются весьма веские причины. КМДП ИМС - это в высшей степени универсальные и легко применяемые устройства, которые обладают уникальными свойствами, нехарактерными для других классов цифровых ИМС.

Комплементарными эти ИМС названы потому, что они изготовлены на основе КМДП транзисторов, т.е. на основе пар полевых транзисторов со структурой: металл - окисел(диэлектрик) - полупроводник, имеющих очень близкие характеристики и каналы разных типов проводимости. ИМС, построенные по такому принципу потребляют от источника питания существенно меньшую мощность, чем все другие ИМС и могут работать в более широком диапазоне уровней питающих напряжений. Электронные наручные часы и устройства для автомобиля, медицинские электронные приборы, телевизионные приемники, портативные калькуляторы - это лишь немногие примеры устройств, в которых используются КМДП ИМС.

Основные достоинства цифровых ИМС на КМОП-структурах - большое входное сопротивление транзисторов (R вх) 10 12 Ом) и высокий уровень интеграции. При выполнении импульсных устройств на интегральных логических элементах КМОП сопротивления времязадающих резисторов вследствие высоких входных сопротивлений транзисторов не ограничены сверху, следовательно, для получения импульсов с большой длительностью не следует увеличивать электрическую емкость времязадающих конденсаторов.

Комплементарные структуры представляют собой взаимодополняющие пары биполярных (p-n-p и n-p-n) или МДП (p-канальных и n-канальных) транзисторов, что позволяет значительно улучшить характеристики ИМС. Они изготавливаются на общей подложке в карманах, изолированных от подложки либо p-n -переходом, либо диэлектрической пленкой. Комплементарные транзисторы выполняются в виде горизонтальной и вертикальной структур.

В транзисторах горизонтальной структуры эмиттер, база, и коллектор расположены на одной горизонтальной плоскости, поэтому инжектированные в базу неосновные носители перемещаются не перпендикулярно поверхности кристалла, а вдоль нее. Такие транзисторы называются торцевыми (латеральными). При изготовлении торцевых

транзисторов p-n-p - типа формирование эмиттеров осуществляется во время базовой диффузии n-p-n - транзисторов. Затем путем второй базовой диффузии эмиттер p-n-p - транзистора окружается коллектором. Базой транзистора служит исходный слой полупроводника n-типа между этими областями. Ширина базы, следовательно, и значение коэффициента передачи тока базы и определяются расстоянием между окнами, протравливаемыми в фоторежиме для эмиттера и коллектора.

В вертикальных структурах база располагается под эмиттером (инжектированные неосновные носители перемещаются в направлении, перпендикулярном поверхности кристалла). Все три области p-n-p - транзистора (коллектор, база и эмиттер) формируются путем диффузии. Такие комплементарные структуры сложны в изготовлении из-за высоких требований точности концентрации легирующих примесей. Однако транзисторы, изготовленные по такой технологии, имеют больший, чем транзисторы с горизонтальной структурой козффициент передачи тока базы и и высокое напряжение пробоя коллекторного перехода.

КМОП(комплементарная структура металл-оксид-полупроводник)- технология построения электронных схем. В более общем случае - КМДП (со структурой металл-диэлектрик-полупроводник). Отличительной особенностью схем КМОП по сравнению с биполярными технологиями (ТТЛ, ЭСЛ и др.) является очень малое энергопотребление в статическом режиме (в большинстве случаев можно считать, что энергия потребляется только во время переключения состояний)

Подавляющее большинство современных логических микросхем, в том числе процессоров, используют схемотехнику КМОП. В технологии КМОП используются полевые транзисторы с изолированным затвором с каналами разной проводимости.

В устройствах на микросхемах КМОП вполне применимы меры по борьбе с дребезгом, известные из опыта работы с микросхемами ТТЛ, например, включение статического триггера на двух элементах И-НЕ или ИЛИ-НЕ. Однако чрезвычайно высокое входное сопротивление микросхем КМОП (порядка сотен и тысяч мегаом) и относительно высокое выходное сопротивление (сотни ом - один килоом) позволяет упростить цепи подавления дребезга, исключив резисторы. Вариантом схемы является устройство, собранное всего лишь на одном неинвертирующем логическом элементе.

Здесь следует сказать несколько слов о неинвертирующих логических элементах серий КМОП. Большинство логических элементов этих серий являются инвертирующими. Как указывалось выше, микросхемы, содержащие в своем обозначении буквы «ПУ», служат для согласования микросхем КМОП с микросхемами ТТЛ. По этой причине их выходные токи при подаче на их выходы напряжения питания или соединении выходов с общим проводом в устройстве по схемам могут достигать многих десятков миллиампер, что отрицательно сказывается на надежности устройств и может служить мощным источником помех. Большое входное сопротивление микросхем КМОП позволяет в некоторых случаях обойтись вообще без активных элементов для подавления дребезга.

Наиболее перспективны серии, выполненные на комплементарных МОП-транзисторах (КМОП) (К176, К564 и др.). В них отсутствуют нагрузочные резисторы, а МОП-транзисторы с разной электропроводностью каналов выполняют роль ключей. При напряжении на затворах, большем порогового, для транзисторов с каналом определенного типа соответствующий транзистор отперт, а другой заперт. При другом значении большем порогового для транзисторов с электропроводностью противоположного типа отпертый и запертый транзисторы меняются местами. Такие структуры успешно работают при изменении в широких пределах напряжения источника питания (от 3 до 15 В), что недостижимо для логических элементов, в состав которых входят резисторы. В статическом режиме при большом сопротивлении нагрузки логические элементы КМОП практически не потребляют мощности.

Для них также характерны: стабильность уровней входного сигнала и малое его отличие от напряжений источника питания; высокое входное и небольшое выходное сопротивления; хорошая помехоустойчивость; легкость согласования с микросхемами других серий.

Логические элементы КМОП, выполняющие функцию 3 И-НЕ. В нем использованы транзисторы с индуцированным каналом. Транзисторы VT1-VT3 имеют канал -типа и открыты при напряжении затворов, близких к нулю. Транзисторы имеют канал -типа и открыты при напряжениях затворов, больших порогового значения.

При нулевом входном сигнале хотя бы на одном из входов логического элемента один из транзисторов открыт и выходное напряжение равное Е. И только в том случае, если на всех входах есть сигнал логической единицы (обычно равный Е), все транзисторы VT1 - закрыты, а ярусно включенные транзисторы открыты. Выходное напряжение равно потенциалу общей шины (логический 0). Таким образом, сочетание ярусного включения транзисторов с каналами, имеющими один тип электропроводности, и параллельного соединения транзисторов с каналами другого типа электропроводности позволили реализовать функцию И-НЕ.

Если группы ярусно и параллельно включенных транзисторов поменять местами, то будет реализован элемент, выполняющий функцию. Он работает аналогично предыдущему. Транзисторы открыты в том случае, если на их затворах логическая 1, и заперты при входных сигналах логического 0.

Из рассмотренных схем видно, что в статическом режиме один из транзисторов, включенных последовательно, всегда закрыт, а другой открыт. Так как закрытый транзистор имеет большое сопротивление, то ток в цепи определяется только малыми значениями токов утечек и микросхема практически не потребляет электрическую мощность.

В качестве базового инвертора, устанавливаемого на входе ЛЭ, обычно используется цепь. Для предотвращения пробоя пленки оксида под затворами МОП-транзисторов схему инвертора обычно дополняют диодами, выполняющими защитные функции. Постоянная времени этих компонентов около 10 не. Поэтому их введение существенно не меняет динамические характеристики логических элементов. При попадании в цепь входа статических напряжений той или иной полярности соответствующие диоды открываются и закорачивают на цепь источника питания источник статического заряда. Резистор, который вместе с барьерными емкостями диодов образует интегрирующую цепь, уменьшает скорость увеличения напряжения на затворе до значения, при котором диоды VD2, VD3 успевают открыться.

Если источник напряжения имеет малое внутреннее сопротивление, то через диод при потечет большой прямой ток. Поэтому при включении аппаратуры с подобными логическими элементами напряжение питания должно подаваться раньше входного сигнала, а при выключении - наоборот. В тех случаях, когда допустимо некоторое снижение быстродействия, в цепь входа можно включать резисторы, ограничивающие входной ток на уровне.

В ряде микросхем для увеличения крутизны передаточной функции и повышения нагрузочной способности к выходу инвертора логического элемента подключают один или два дополнительных инвертора. Транзисторы дополнительного инвертора имеют повышенную мощность. За счет них обеспечивается уменьшение сопротивлений каналов открытых выходных транзисторов инвертора с кОм до кОм. Эти значения выходных сопротивлений позволяют не вводить в выходные цепи токоограничивающие резисторы, защищающие от короткого замыкания на выходе.

В логических элементах КМОП предельно просто реализуют элементы с тремя устойчивыми состояниями. Для этого последовательно с транзисторами инвертора включают два комплементарных транзистора,управляемых инверсными сигналами. Если при подаче сигналов транзисторы закрыты, то выходное сопротивление инвертора имеет большое значение (инвертор находится в третьем высокоимпедансном состоянии).

Третье состояние имеется у отдельных микросхем, например у логических элементов типа, а также у сложных функциональных узлов серий КМОП.

Согласование логических элементов ТТЛ с логическими элементами КМОП можно выполнить несколькими способами:

1) питать логические элементы КМОП малыми напряжениями, при которых сигналы логических элементов ТТЛ переключают транзисторы логических элементов КМОП;

2) использовать логические элементы ТТЛ с открытым коллектором, в цепь выхода которых включен резистор, подключенный к дополнительному источнику напряжения;

3) применять микросхемы преобразователей уровня при согласовании серий КМОП с сериями ТТЛ и при согласовании серий ТТЛ с сериями КМОП).

При необходимости увеличить выходную мощность допускается параллельное соединение нескольких микросхем. Для подавления помех по цепи питания между шинами питания включают электролитический конденсатор емкостью и параллельно ему керамические конденсаторы емкостью на корпус. Последние подключают непосредственно к выходам микросхем. Емкость нагрузки, как правило, не должна превышать. При большем значении емкости нагрузки последовательно с выходом устанавливают дополнительный резистор, ограничивающий ток ее переразрядки. При наличии выбросов напряжения во входном сигнале последовательно с входом ЛЭ можно включить ограничительный резистор номиналом до 10 кОм. Неиспользованные входы ЛЭ следует обязательно подключать к шинам источника питания или соединять параллельно с подключенными входами. В противном случае возможны пробои диэлектрика под затвором и нарушение работоспособности вследствие сильного влияния помех.

Допускается кратковременное замыкание накоротко выходных зажимов микросхем при малом напряжении питания.

При хранении и монтаже следует опасаться статического электричества. Поэтому при хранении выводы электрически замыкают между собой. Монтаж их проводится при выключенном напряжении питания, причем обязательно использование браслетов, с помощью которых тело электромонтажников соединяется с землей.

Логические элементы КМОП-серий широко применяются при построении экономичных цифровых устройств малого и среднего быстродействия. В дальнейшем по мере усовершенствования технологии их изготовления они могут составить конкуренцию для логических элементов ТТЛ при создании быстродействующих устройств.

Обычно при конструировании пробников и калибраторов используют генераторы коротких импульсов, вырабатывающие сигнал с широким и равномерным спектром. Такой сигнал позволяет быстро проверять каскады радиоаппаратуры, как низкочастотные (НЧ), так и высокочастотные (ВЧ). Причем чем меньше длительность импульсов, тем лучше - спектр получается шире и равномернее.

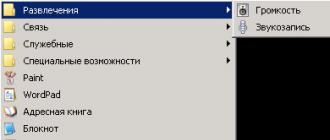

Как правило, подобные генераторы состоят из двух основных узлов: собственно генератор прямоугольных импульсов и формирователь коротких импульсов. Между тем можно обойтись без специального формирователя, поскольку он уже имеется в логическом элементе микросхемы структуры КМОП.

Рассмотрим схему

Рисунок 4- RC- генератор

На рисунке 4 показан известный RC-генератор, работающий в данном случае на частоте около 1000 Гц (она зависит от номиналов деталей R1, С1). Низкочастотный сигнал прямоугольной формы поступает с выхода элемента DD1.2 (вывод 4) через цепочку R2C3 на переменный резистор R4 - им плавно регулируют амплитуду сигнала, подаваемого на проверяемый узел.

Выход же высокочастотного сигнала (коротких импульсов) выполнен несколько необычно - сигнал снимают с переменного резистора R3, включенного в цепь питания микросхемы. Перемещением движка этого резистора плавно регулируют уровень выходного высокочастотного сигнала.

Рассмотрим принцип работы такого формирователя по упрощенной схеме логического элемента структуры КМОП, показанного на рисунке 5.

Рисунок 5-упрощенная схема логического элемента структуры КМОП

Его основа - два последовательно включенных полевых транзистора с изолированным затвором и разным типом проводимости каналов. Если последовательно с транзисторами включить резистор R1, а на вход элемента подавать прямоугольные импульсы U1, произойдет следующее (рис. 3). Из-за того, что длительность фронта импульса не может быть бесконечно малой, а также из-за инерционности транзисторов, в момент действия фронта наступит такой момент, когда оба транзистора окажутся в открытом состоянии. Через них потечет так называемый сквозной ток, значение которого может составлять от единиц до десятков миллиампер в зависимости от типа микросхемы и напряжения источника питания. На резисторе будут формироваться короткие импульсы напряжения U2. Причем как в момент действия фронта, так и спада.

Иначе говоря, произойдет удвоение частоты исходных импульсов.

Сопротивление резистора не должно быть большим во избежание нарушения режима работы элементов микросхемы. Это означает, что к высокочастотному выходу можно подключать низкоомную нагрузку сопротивлением 50...75 Ом.

У рассмотренного генератора максимальная амплитуда импульсов на высокочастотном выходе составляет 100...150мВ, а потребляемый от источника питания ток не превышает 1,6 мА. Генератор рассчитан на использование при проверке усилителей ЗЧ, трехпрограммных громкоговорителей, радиоприемников на диапазонах ДВ и СВ.

структуры КМОП

Полевой транзистор - полупроводниковый прибор, через который протекает поток основных носителей зарядов, регулируемый поперечным электрическим полем, которое создаётся напряжением, приложенным между затвором и стоком или между затвором и истоком.

Так как принцип действия полевых транзисторов основан на перемещении основных носителей заряда одного типа (электронами или дырками), такие приборы ещё называют униполярными, тем самым противопоставляя их биполярным.

Полевые транзисторы классифицируют на приборы с управляющим p-n-переходом и с изолированным затвором, так называемые МДП («металл-диэлектрик-полупроводник»)-транзисторы, которые также называют МОП («металл-оксид-полупроводник»)-транзисторами, причём последние подразделяют на транзисторы со встроенным каналом и приборы с индуцированным каналом.

К основным параметрам полевых транзисторов причисляют: входное сопротивление, внутреннее сопротивление транзистора, также называемое выходным, крутизну стокозатворной характеристики, напряжение отсечки и некоторые другие.

Полевой транзистор с управляющим p-n-переходом - это полевой транзистор, в котором пластина из полупроводника, например n-типа, имеет на противоположных концах электроды (сток и исток), с помощью которых она включена в управляемую цепь. Управляющая цепь подключается к третьему электроду (затвору) и образуется областью с другим типом проводимости, в данном случае p-типом.

Источник питания, включенный во входную цепь, создаёт на единственном p-n-переходе обратное напряжение. Во входную цепь также включается и источник усиливаемых колебаний. При изменении входного напряжения изменяется обратное напряжение на p-n-переходе, в связи с чем меняется толщина обедненного слоя (n-канал), то есть площадь поперечного сечения области, через которую проходит поток основных носителей заряда. Эта область называется каналом.

Отличительной особенностью структуры КМОП по сравнению с другими МОП-структурами (N-МОП, P-МОП) является наличие как n-, так и p-канальных полевых транзисторов; как следствие, КМОП-схемы обладают более высокой скоростью действия и меньшим энергопотреблением, однако при этом характеризуются более сложным технологическим процессом изготовления и меньшей плотностью упаковки.